ADS42LB49

ADS42LB49 is Analog-to-Digital Converter manufactured by Texas Instruments.

Features

- 1 Dual Channel

- 14- and 16-Bit Resolution

- Maximum Clock Rate: 250 MSPS

- Analog Input Buffer with High Impedance Input

- Flexible Input Clock Buffer with

Divide-by-1, -2, and -4

- 2-VPP and 2.5-VPP Differential Full-Scale Input

(SPI-Programmable)

- DDR or QDR LVDS Interface

- 64-Pin VQFN Package (9-mm × 9-mm)

- Power Dissipation: 820 m W/ch

- Aperture Jitter: 85 f S

- Internal Dither

- Channel Isolation: 100 d B

- Performance at f IN = 170 MHz at 2 VPP,

- 1 d BFS

- SNR: 73.2 d BFS

- SFDR:

- 87 d Bc (HD2 and HD3)

- 100 d Bc (Non HD2 and HD3)

- Performance at f IN = 170 MHz: 2.5 VPP,

- 1 d BFS

- SNR: 74.9 d BFS

- SFDR:

- 85 d Bc (HD2 and HD3)

- 97 d Bc (Non HD2 and HD3)

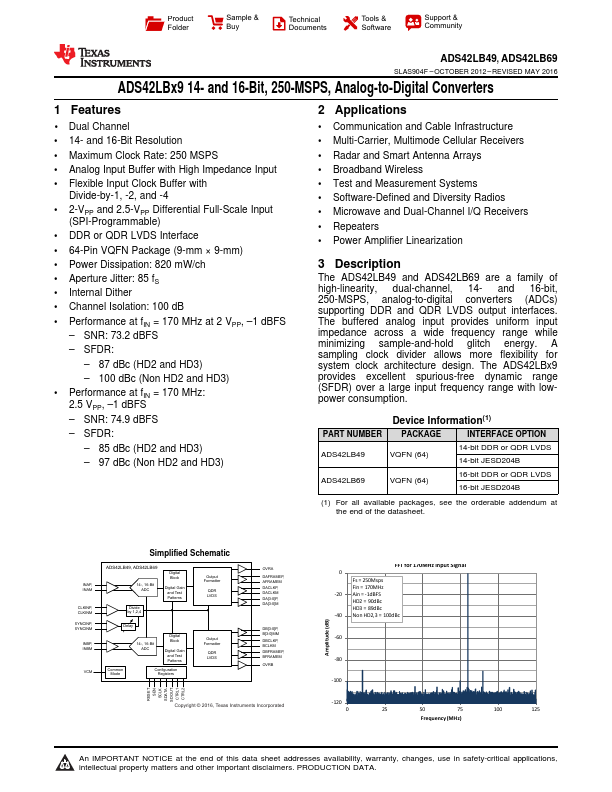

INAP, INAM

CLKINP, CLKINM SYNCINP, SYNCINM

INBP, INBM

Simplified Schematic

ADS42LB49, ADS42LB69

14-, 16-Bit ADC

Digital Block

Digital Gain and Test Patterns

Divide by 1,2,4

Output Formatter

QDR LVDS

Delay mon...